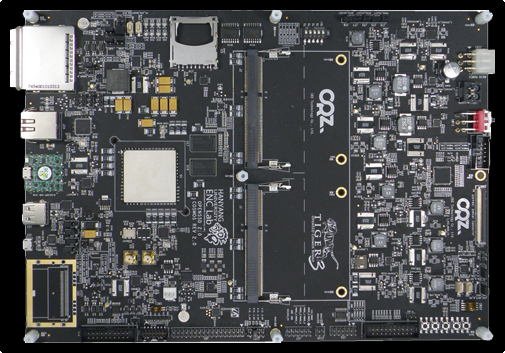

Hardware Specification

The Cosmos OpenSSD platform consists of the following components:

The Cosmos OpenSSD platform consists of the following components:

- HYU Tiger3 SSD controller

- Implemented by XC7Z045-FFG900-3 Zynq-7000 FPGA

- Dual 1GHz ARM Cortex-A9 core

- Neon DSP Co-processor for each core

- 350K LCs

- Memory

- 1GByte DDR3 SDRAM

- Dual QSPI Flash Memory

- 1 SD Card Slot

- Host interface

- Dual PCIe Gen2 x8 End-Points (Cabled PCIe Interface)

- One PCIe Gen2 x8 can be configurable to RC

- Connectivity

- 1 Gigabit Ethernet Interface

- 1 USB 2.0 (configurable to Host or Device)

- Console Debug Interface

- 1 USB-UART Port

- 1 ARM JTAG

- 1 PL JTAG

- 1 Digilent USB-JTAG

- Indicators and Switches

- LEDs and Tactile Switches

- NAND Flash Interface

- 2x SO-DIMM NAND Flash Slots

- 4-way NAND Flash Interface for each slot

- Support for Hynix 128Gbit MLC NAND

- Support for flash memory from other manufacturers planned

Software/Firmware/RTL

The Cosmos OpenSSD platform will include the following software/firmware/RTL packages. The latest version can be downloaded from https://github.com/Cosmos-OpenSSD/Cosmos-OpenSSD.

- Basic firmware source code for interfacing with PCIe controller and Flash controller

- Source codes of three sample FTLs (TutorialFTL, GreedyFTL, and DummyFTL)

- Source code of the sample host-side device drivers (Linux and Windows)

- RTL source code of the sample Tiger3 controller hardware