Hardware Specification

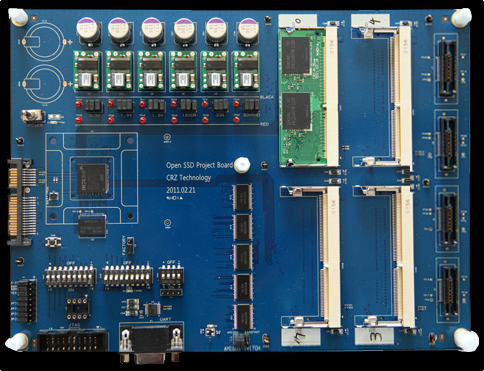

The Jasmine evaluation board consists of the following components:

The Jasmine evaluation board consists of the following components:

- Indilinx BarefootTM controller

- ARM7TDMI-S core running at up to 87.5MHz

- 96KB internal SRAM

- SATA 2.0 host interface (3Gbps) with NCQ support

- Mobile SDRAM controller up to 64MB (running at up to 175MHz)

- NAND flash BCH 8/12/16 bit correction per sector

- SDRAM Reed Solomon 2 byte correction per 128 + 4 byte

- NAND flash controller up to 64 CE’s (4 channels, 16 bits/channel, 8 banks/channel)

- Separate DRAM access bus for transferring data between NAND flash memory and DRAM buffer

- Supports various NAND flash memory chips from different vendors such as Samsung, Hynix, Toshiba, Micron, etc.

- Specialized hardware for buffer management, flash control, and memory utility functions

- Debugging/monitoring aids:

- JTAG

- UART

- 1 LED and 6 GPIO pins

- Mictor connector to NAND flash signals for logic analyzer

- Separate current measurement points for core, I/O, SDRAM, and NAND

- Mobile SDRAM

- 64MB from Samsung (subject to change)

- 8 NAND flash memory slots

- 64GB from Samsung (subject to change) in two NAND flash modules

- Each flash module has four 8GB NAND packages (Samsung K9LCG08U1M, 35nm asynchronous mode MLC NAND)

- Each package has two 4GB dies with two CE signals (Dual Die Package)

Software

The software package for the Jasmine OpenSSD Platform consists of the followings. The latest version can be downloaded from https://github.com/openssd/jasmine.

- Basic firmware source code for interfacing with SATA controller and Flash controller

- LLD (Low-Level Driver) library

- Source codes of three sample FTLs: TutorialFTL, GreedyFTL, and DummyFTL